## (11) EP 0 789 867 B1

### (12) EUROPEAN PATENT SPECIFICATION

DE CONNEXION D'UN ENSEMBLE DE BUS SERIE HIERARCHIQUE

(45) Date of publication and mention of the grant of the patent:07.12.2011 Bulletin 2011/49

(21) Application number: 95937703.7

(22) Date of filing: 31.10.1995

(51) Int Cl.: **G06F** 9/02 (2006.01) **G06F** 13/42 (2006.01)

(86) International application number: PCT/US1995/014242

(87) International publication number: WO 1996/013769 (09.05.1996 Gazette 1996/21)

# (54) M & A FOR DYNAMICALLY DETERMINING AND MANAGING CONNECTION TOPOLOGY OF A HIERARCHICAL SERIAL BUS ASSEMBLY

VERFAHREN UND VORRICHTUNG FÜR DIE DYNAMISCHE BESTIMMUNG UND VERWALTUNG DER VERBINDUNGSTOPOLOGIE EINER HIERARCHISCHEN SERIELLEN BUSVORRICHTUNG PROCEDE ET APPAREIL DE DETERMINATION ET GESTION DYNAMIQUE DE LA TOPOLOGIE

- (84) Designated Contracting States: **DE GB IT NL**

- (30) Priority: 31.10.1994 US 332375

- (43) Date of publication of application: 20.08.1997 Bulletin 1997/34

- (73) Proprietor: Intel Corporation Santa Clara, CA 95052 (US)

- (72) Inventors:

- KNOLL, Shaun Portland, OR 97209 (US)

- MORRISS, Jeff, Charles Boulder Creek, CA 95006 (US)

- CALLAHAN, Shelagh Beaverton, OR 97006 (US)

- BHATT, Ajay, V. El Dorado Hills, CA 95762 (US)

- CADAMBI, Sudarshan, Bala Portland, OR 97229 (US)

- (74) Representative: Wombwell, Francis et al Potts, Kerr & Co.

15, Hamilton Square Birkenhead Merseyside CH41 6BR (GB)

- (56) References cited: **US-A- 5 394 556**

- IEEE, "High Performance Serial Bus", P1394/Draft 6.2v0, June 1993, pg. 151-155.

P 0 789 867 B

Note: Within nine months of the publication of the mention of the grant of the European patent in the European Patent Bulletin, any person may give notice to the European Patent Office of opposition to that patent, in accordance with the Implementing Regulations. Notice of opposition shall not be deemed to have been filed until the opposition fee has been paid. (Art. 99(1) European Patent Convention).

#### Description

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

**[0001]** The present invention relates to the field of computer systems. More specifically, the present invention relates to serial buses for connecting peripherals to the system units of computer systems, including the associated controllers and interfaces.

1

#### 2. Background Information

[0002] A number of interrelated considerations is making it desirable to have a single, relatively fast, bi-directional, isochronous, low-cost, and dynamically configurable serial bus for simultaneously connecting isochronous as well as asynchronous peripherals to the system unit of a desktop computer system. Isochronous peripherals are peripherals that generate real time natural data such as voice, motion video, and the like. These interrelated considerations include:

#### Connection of the Telephone to the Desktop Computer

[0003] It is expected that the merging of computing and communication will be the basis of the next generation of productivity applications on desktop computers. The movement of machine oriented and human oriented data types from one location or environment to another depends on ubiquitous and cheap connectivity. Unfortunately, the computing and communication industries have evolved independently. As a result, a wide range of desktop computer and telephone interconnects have to be supported.

#### Ease of Use

[0004] The lack of flexibility in reconfiguring desktop computers has been acknowledged as its Achilles heel to it's further development. The combination of user friendly graphical interfaces and the hardware and software mechanisms associated with the new generation of system bus architectures have made desktop computers less confrontational and easier to reconfigure. However, from the enduser point of view, the desktop computer's I/O interfaces such as serial/parallel ports, keyboard/mouse/joystick interfaces, still lack the attributes of plug and play or are too limiting in terms of the type of I/O devices that can be live attached/detached.

#### Port Expansion

**[0005]** The addition of external peripherals to desktop computers continues to be constrained by port availability. The lack of a bi-directional, low-cost, low to mid speed peripheral bus has held back the proliferation of periph-

erals like telephone/fax/modem adapters, answering machines, scanners, personal digital assistants (PDA), keyboards, mice, etc. Existing interconnects are optimized for one or two point products. As each new function or capability is added to the desktop computer, typically a new interface has been defined to address this need.

[0006] In other words, this desired serial bus is expected to provide low cost simultaneous connectivity for the

ed to provide low cost simultaneous connectivity for the relatively low speed 10-100 kbps interactive devices such as keyboard, mouse, stylus, game peripherals, virtual reality peripherals, and monitors, as well as the moderate speed 500 - 5000 kbps isochronous devices such as IS-DN, PBX, POTS, and other audio devices. A multiplicity of both types of devices are expected to be connected and active at the same time, and yet the latter type of devices are provided with guaranteed latencies and bandwidths. Furthermore, the devices are expected to be hot attached and detached, with the serial interface being able to dynamically reconfigure itself without interrupting operation of the desktop computer system.

**[0007]** There are several technologies that are commonly considered to be serial buses for connecting peripherals to system units of computer systems. Each of these buses is designed to handle a specific range of communications between system units and peripherals. Particular examples of these buses include:

Apple® Desktop Bus (ADB): ADB is a proprietary bus of Apple Computer Inc. It is a minimalist serial bus that provides a simple read/write protocol to up to 16 devices. Only basic functions are required of the controller and interface hardware. Thus, the implementation cost is expected to be low. However, ADB supports data rates only up to 90 kbps, just enough to communicate with asynchronous desktop devices such as keyboards and mice. It is not capable of simultaneously supporting the moderate speed isochronous devices discussed earlier.

Access.bus (A.b): A.b is developed by the Access.bus Industry Group. It is based on the I2C technology of Philips Corporation and a software model of Digital Equipment Corporation (DEC). A.b is also designed primarily for asynchronous devices such as keyboards and mice. However A.b is generally considered to be more versatile than ADB. A.b's protocol has well defined specifications for dynamic attach, arbitration, data packets, configuration and software interface. Moderate amounts of functions are required of the controller and interface hardware. Thus, the implementation cost is only marginally competitive for the desired desktop application. While addressing is provided for up to 127 devices, the practical loading is limited by cable lengths and power distribution considerations. Revision 2.2 specifies the bus for 100 kbps operation, but the technology has headroom to go up to 400 kbps using the same separate clock and data wires. However, at 400 kbps, A.b still falls short in meeting the requirements of the moderate speed isochronous devices.

IEEE's P1394 Serial Bus Specification (aka FireWire): FireWire is a high performance serial bus. It is designed primarily for hard disk and video peripherals, which may require bus bandwidth in excess of 100 Mbps. It's protocol supports both isochronous and asynchronous transfers over the same set of 4 signal wires, broken up as differential pairs of clock and data signals. Thus, it is capable of simultaneously meeting the requirements of low speed interactive as well as moderate speed isochronous devices. However, elaborate functions are required of the controller and interface hardware, rendering FireWire to be non-price competitive for the desired desktop application. Moreover, the first generation of devices, based on FireWire's specification, are only just becoming available in the market.

The Concentration Highway Interface (CHI): CHI is developed by American Telephone & Telegraph Corporation (AT&T) for terminals and digital switches. It is a full duplex time division multiplexed serial interface for digitized voice transfer in a communication system. The protocol consists of a number of fixed time slots that can carry voice data and control information. The current specification supports data transfer rates up to 4,096 Mbps. The CHI bus has 4 signal wires: Clock, Framing, Receive Data, and Transmit Data. Both, the Framing and the Clock signals are generated centrally (i.e. PBX switch). Thus, it is also capable of simultaneously meeting the requirements of low speed interactive as well as the moderate speed isochronous devices. Similar to FireWire, elaborate functions are also required of the controller and interface hardware. As a result, CHI is also non-price competitive for the desired desktop application.

[0008] US 5,394,556 (Oprescu) discloses a method and apparatus for unique address assignment to the nodes of a communication bus once the nodes are configured into an acyclic directed graph. Oprescu allegedly configures the nodes into the acyclic graph by establishing parent child relationships for each pair of interconnected nodes. The address assignment process begins from each leaf that sends a request to its parent which waits to receive requests from all its leaf children. As a result, all leaf nodes self-assig a unique physical address to themselves. However, Oprescu's node assignment process is neither efficient nor conducive to dynamically maintain a connection topology of nodes when nodes are being dynamically plugs or unplugged from the communication bus because Oprescu allegedly makes it necessary to reconfigure the graph, resulting in bus initialization, when a branch node is disengaged.

[0009] WO94/15303 allegedly discloses a method and apparatus for unique address assignment, node selfidentification and topology mapping for a directed acyclic graph. WO94/15303 allegedly configures the nodes into the acyclic graph by establishing parent child relationships for each pair of interconnected nodes. The address assignment process begins from each leaf that sends a request to its parent which waits to receive requests from all its leaf children. As a result, all leaf nodes self-assign a unique physical address to themselves. WO94/15303's node assignment process is neither efficient nor conductive to dynamically maintain a connection topology of nodes when nodes are being dynamically plugged or unplugged from the communication bus because WO94/15303 allegedly makes it necessary to reconfigure the graph, resulting in bus initialization, when a branch node is disengaged.

**[0010]** As will be disclosed in more detail below, the present invention provides the desired serial bus assembly, including its associated controller, bridging connectors and interfaces, that advantageously overcomes the limitations of the prior art serial buses in a novel manner.

#### SUMMARY OF THE INVENTION

[0011] The present invention includes circuitry and complementary logic provided to a bus controller, a number of 1:n bus signal distributors, and a number of bus interfaces of an hierarchical serial bus assembly for the bus controller to dynamically detect and manage the interconnection topology of the serial bus elements. The serial bus assembly is used to serially interface a number of isochronous and asynchronous peripherals to the system unit of a computer system. These circuitry and complementary logic support an hierarchical view of the serial bus elements, logically dividing the hierarchy into multiple tiers. This logical view of the serial bus elements is used by the bus controller to detect the presence of interconnected serial bus elements and the functions of the bus agents, i.e. the system unit and the interconnected peripheral, as well as assignment of addresses to the serial bus elements and the functions at power on, reset, and during operation when serial bus elements are hot attached to or detached from the serial bus assembly.

[0012] Typically, the bus controller is disposed in the system unit, and the bus interfaces are disposed in the connecting peripherals, one bus interface per connecting peripheral. The peripherals, through their bus interfaces, are connected to the system unit through the bus controller, using one or more bus signal distributors disposed in the system unit, stand alone bridging connectors and/or the connecting peripherals. A bus interface is always a termination point. Only a bus signal distributor may have one or more bus signal distributor(s) and/or bus interface(s) connected upstream to rt. Together, the system unit, the serial bus elements, and the peripherals form an hierarchy of interconnected devices, with the system unit and its bus controller logically occupying a root

40

50

tier, the first bus signal distributor connected to the bus controller logically occupying tier zero, the bus signal distributor(s) and/or the bus interface(s) and its/their "host" peripheral(s) connected to the first bus signal distributor logically occupying tier one, and so forth.

5

[0013] A connecting peripheral may be an isochronous or an asynchronous peripheral. Furthermore, a connecting peripheral may be a multi-function peripheral, i.e. multiple functions being mapped to a single bus connection point serviced by a single bus interface.

[0014] At power on or reset, using the hierarchical view, the bus controller systematically detects the presence of the serial bus elements, and the functions of the interconnected peripherals, one logical tier at a time. As the presence of a serial bus element is detected, the bus controller assigns a geographical address to the serial bus element. Additionally, the bus controller systematically assigns a logical address to each function of each interconnected peripheral. Preferably, a bus signal distributor identity and its upstream port may be inferred from the bus signal distributor's assigned geographical address. Furthermore, the connecting bus signal distributor of a bus interface, including the connecting port, may be inferred from the geographical address assigned to the bus interface.

[0015] Similarly, during operation, using the hierarchical view, the bus controller systematically detects live attachment and detachment of serial bus elements, including the functions of the newly interconnected peripherals, one logical tier at a time. As the detachment of a serial bus element is detected, its geographical address is deassigned. If the detached serial bus element is a bus interface, the bus controller also deassigns the logical address(es) assigned to the function(s) of its "host" peripheral. Similarly, as the presence of a newly interconnected serial bus element is detected, the bus controller assigns a geographical address to the newly interconnected serial bus element. If the newly attached serial bus element is a bus interface, the bus controller also assigns a logical address to each function of the newly attached bus interface's "host" peripheral.

[0016] The invention is defined according to the apparatus of claim 1 and the method of claim 12.

#### BRIEF DESCRIPTION OF DRAWINGS

[0017] The present invention will be described by way of exemplary embodiments, but not limitations, illustrated in the accompanying drawings in which like references denote similar elements, and in which:

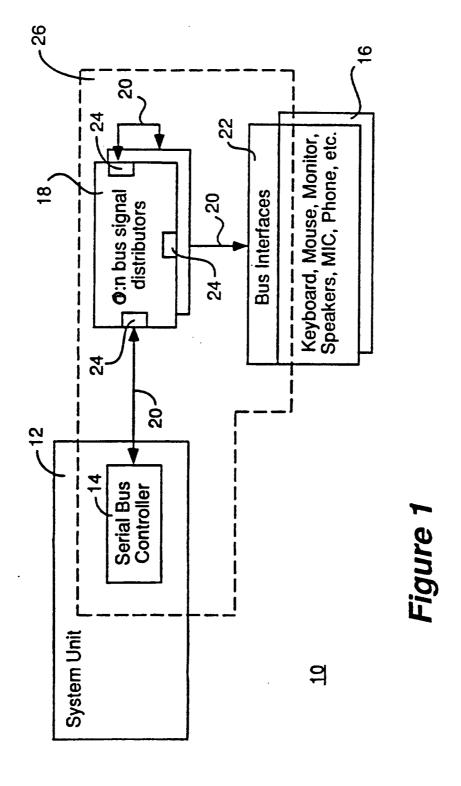

Figure 1 illustrates an exemplary computer system incorporating the serial bus teachings of the present invention:

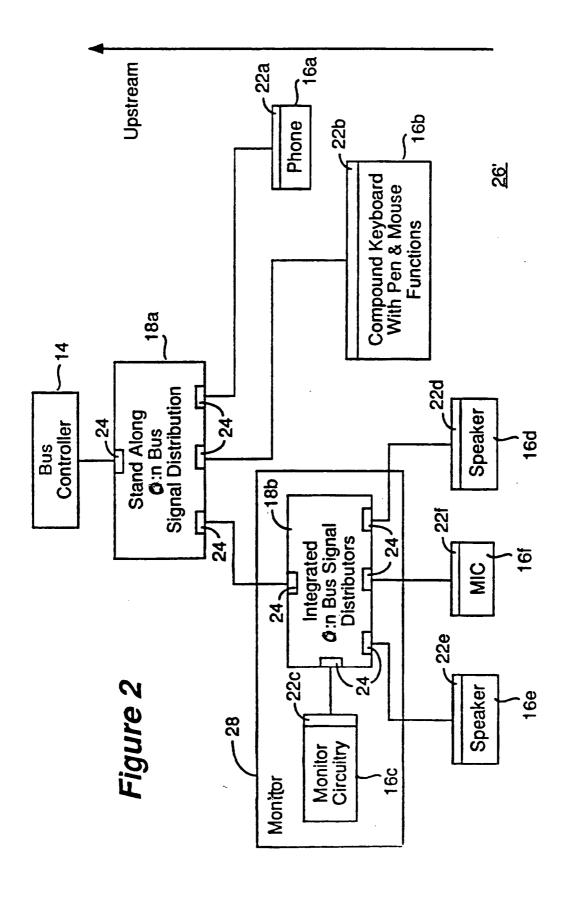

Figures 2 illustrates one embodiment of the serial bus assembly of Figure 1 in further detail;

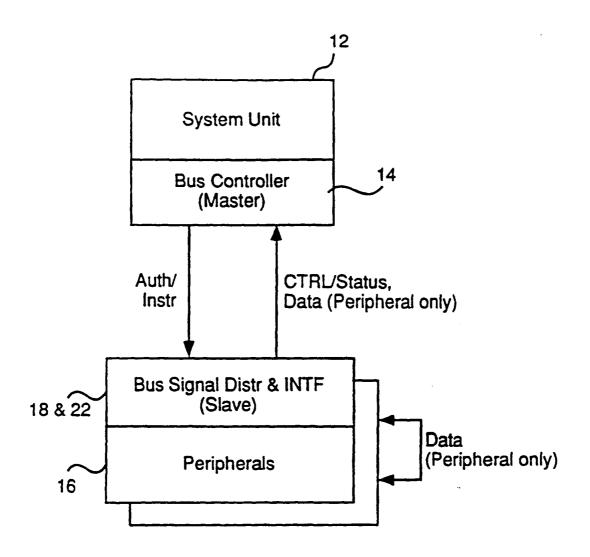

Figure 3 illustrates a master/slave model of flow control employed by the present invention for serially interfacing the interconnected peripherals to the system unit and controlling transaction flows;

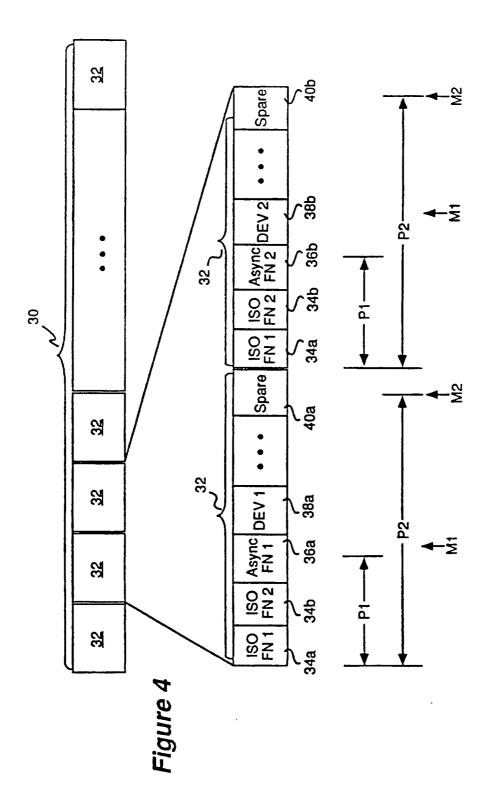

Figure 4 illustrates a frame based polling schedule of the present invention implemented by some embodiments for polling the slave "devices";

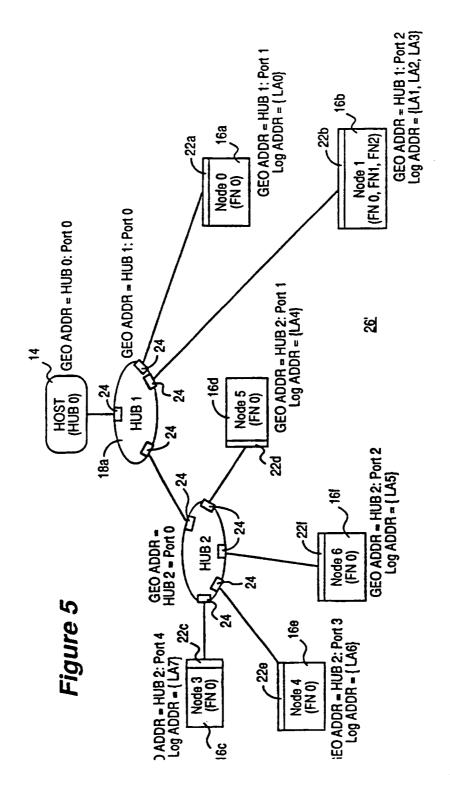

Figure 5 illustrates geographical and logical addressing of the present invention implemented by some embodiments for addressing serial bus elements and functions of bus agents;

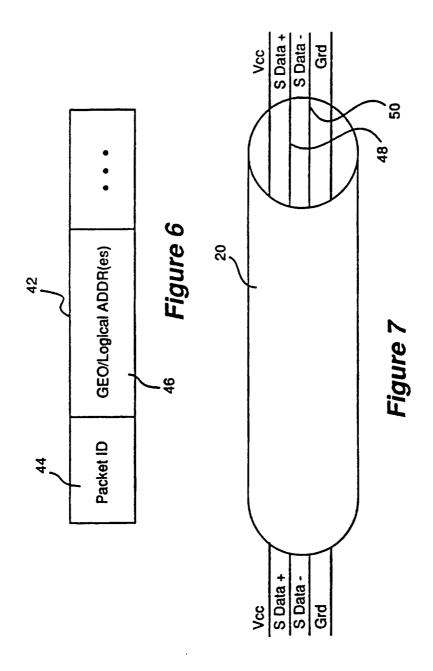

Figure 6 illustrates the essential elements of communication packets of the present invention implemented by some embodiments for conducting transactions employing the master/slave model of flow control;

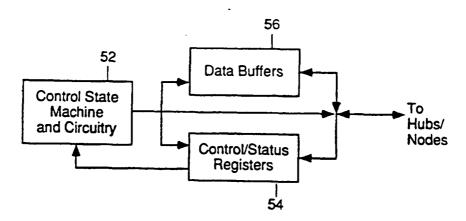

Figure 7 illustrates one embodiment of the cables physically connecting the serial bus elements under the present invention;

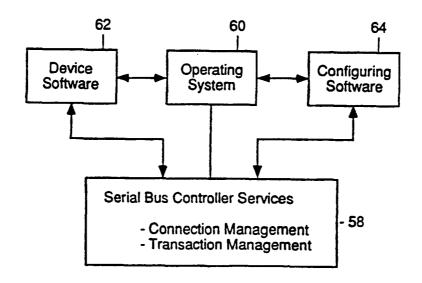

Figures 8-9 illustrate one embodiment of the bus controller of the present invention including its associated software:

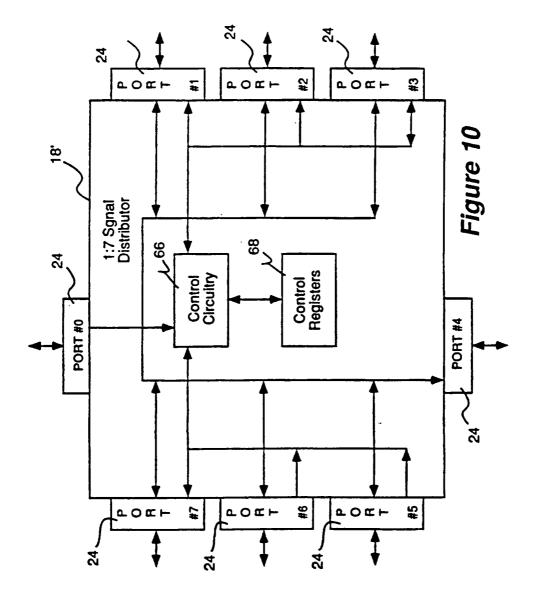

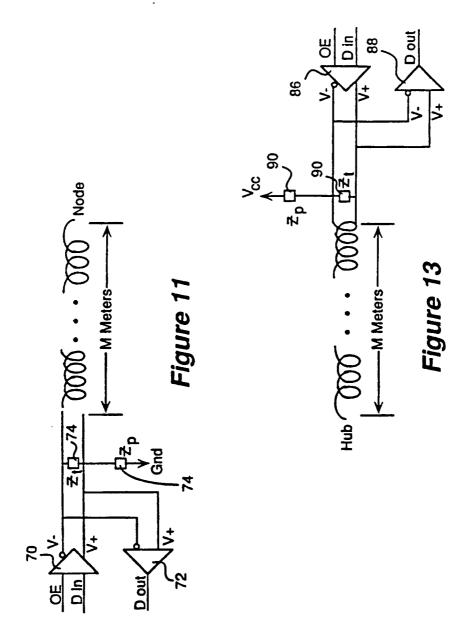

Figures 10-11 illustrate one embodiment of the 1:n bus signal distributor of the present invention including its port circuitry;

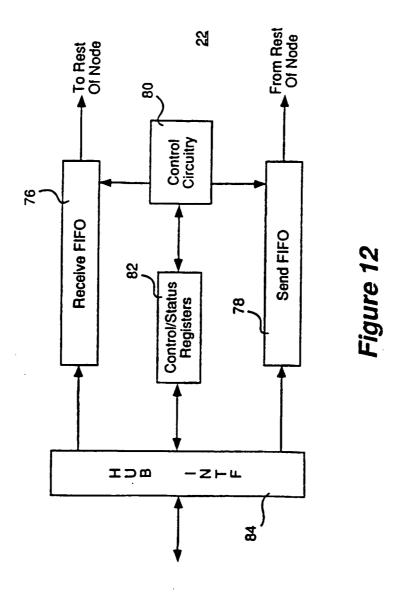

Figures 12-13 illustrate one embodiment of the bus interface of the present invention including its connector circuitry;

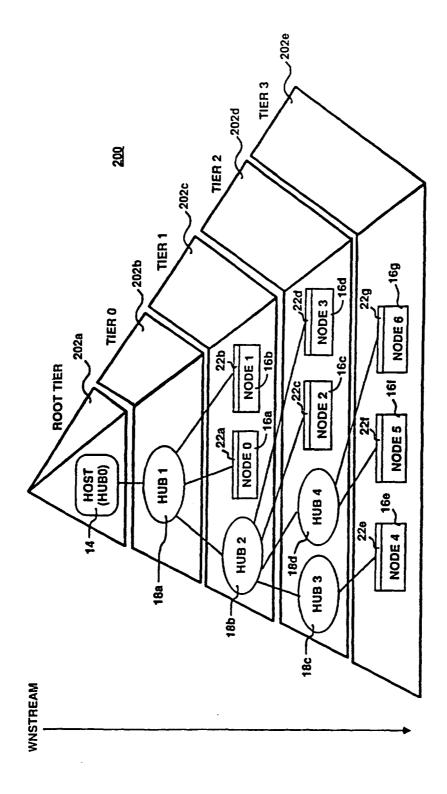

Figure 14 illustrates an hierarchical view of the serial bus elements of the present invention employed by the bus controller for determining and managing connection topology;

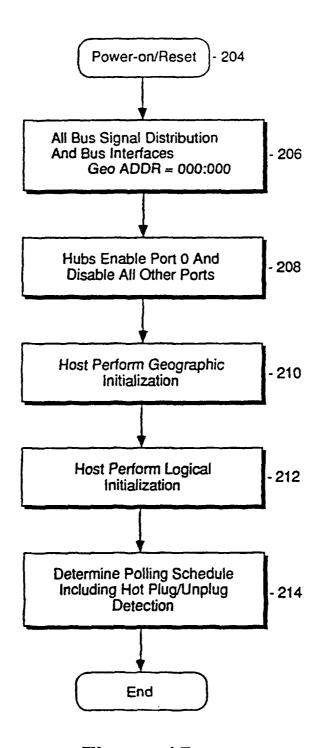

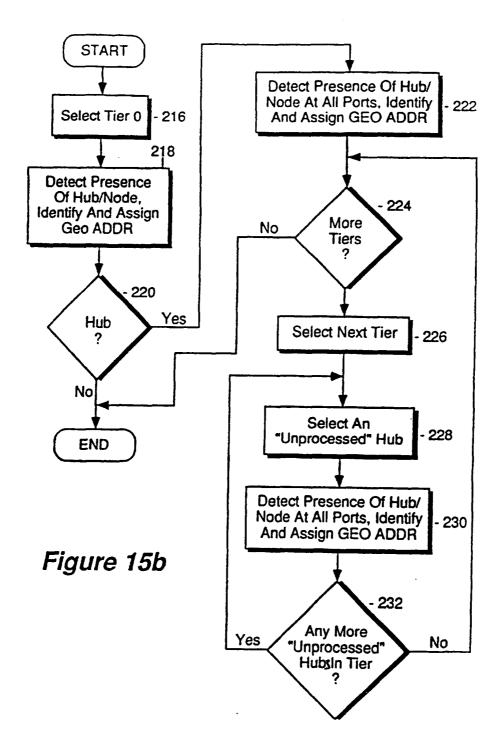

Figures 15a-15c illustrate the collective method steps of the present invention performed by the serial bus elements for determining and managing connection topology at power on or reset, employing the hierarchical view of serial bus elements;

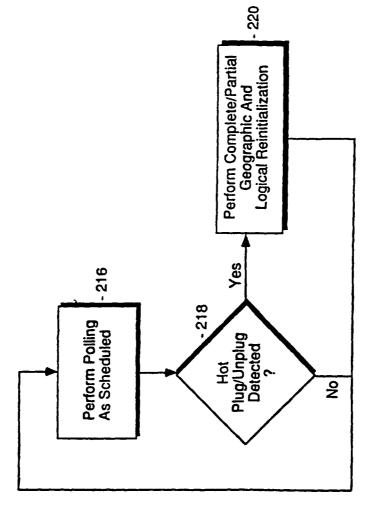

Figure 16 illustrates the collective method steps of the present invention performed by the serial bus elements for managing connection topology during operation.

#### **DETAILED DESCRIPTION**

[0018] In the following description for purposes of explanation, specific numbers, materials and configurations are set forth in order to provide a thorough understanding of the present invention. However, it will be apparent to one skilled in the art that the present invention may be practiced without the specific details. In other instances, well known systems are shown in diagrammatic or block diagram form in order not to obscure the present invention.

Hierarchical Serial Bus Assembly for Serially Interfacing Isochronous and Asynchronous Peripherals to a System Unit of a Computer System

[0019] Referring now to Figure 1, a block diagram illustrating an exemplary computer system incorporating the serial bus teachings of the present invention is shown. Exemplary computer system 10 comprises system unit 12 having serial bus controller 14 of the present invention, 0:n bus signal distributors 18 of the present invention, each having n+1 ports 24, and peripherals 16 having bus interfaces 22 of the present invention. Peripherals 16 are coupled to bus controller 14 of system unit 12 through 0:n bus signal distributors 18 and preferably cables 20. Collectively, bus controller 14, bus signal distributors 18, bus interfaces 22, and cables 20 form a serial bus assembly 26 interconnecting bus agents, i.e. system unit 12 and peripherals 16 to each other.

[0020] Cables 20 are preferably low cost two signal wires cables 48 and 50 (as illustrated in Fig. 7). However, cables 20 are capable of supporting data transfer rates up to 5 Mbps. Furthermore, when such low cost cables 20 are employed, electrical signals are preferably propagated over the two signal wires 48 and 50 between the interconnected devices 14, 18 and 22 in a differential manner. For examples, a negative voltage differential represents a 1-bit and a positive voltage differential represents a O-bit. For some embodiments, data and control states are further inferred from the electrical signals' voltage states and/or durations. A particutar implementation of electrically representing data and control states with voltage states and/or signal durations is described in U.S. 5742847, entitled Method And Apparatus For Serial Bus Elements Of An Hierarchical Serial Bus To Electrically Represent Data And Control States To Each Other.

[0021] Except for bus controller 14, system unit 12 is intended to represent a broad category of system units of computer systems whose constitutions and functions are well known, and will not be otherwise further described. Similarly, except for bus interfaces 22, peripherals 16 are intended to represent a broad category of desktop peripherals, such as keyboards, mouses, monitors, speakers, microphone, telephones whose constitutions and functions are also well known, and will not be otherwise further described either. Bus controller 14, bus signal distributors 18 and bus interfaces 22 will be described in more detail below with additional references to the remaining figures.

[0022] Figures 2 illustrates one embodiment of the serial bus assembly of Figure 1 in further detail. For this embodiment, serial bus assembly 26' includes serial bus controller 14, standalone 0:n bus signal distributor 18a, integrated 0:n bus signal distributor 18b, and bus interfaces 22a - 22f. The serial bus assembly 26' interconnects bus: agents telephone 16a, compound keyboard 16b including keyboard, pen and mouse functions, monitor circuitry 16c of monitor 28, speakers 16d-16e and microphone 16f to system unit 12. Together, the system unit 12, the serial bus elements 14, 18a-18b and 22a-22f, and the interconnected peripherals 16a-16f form an hierarchy of interconnected devices.

[0023] Under the present invention, a bus interface 22a - 22f is allays a termination point. Only a bus signal distributor, e.g. 18a, may have one or more bus signal dis-

tributors, e.g. **18b**, and/or one or more bus interfaces, e.g. **16a**, coupled upstream to it. For the purpose of this disclosure, upstream means "towards the bus controller". Thus, except for the degenerate case where the serial bus assembly **26** has only one connecting peripheral **16**, typically it is a bus signal distributor, such as **18a**, that is connected upstream to the bus controller **14**.

[0024] Furthermore, under the present invention, a connecting peripheral may be an isochronous peripheral, such as telephone 16a, speakers 16d-16e, and microphone 16f, or asynchronous peripherals, such as compound keyboard 16b and monitor 16c. The isochronous peripherals may operate with a data transfer rate as high as 5 Mbps, while the asynchronous peripherals may operate with a data transfer rate as high as 100 kbps. Furthermore, a connecting peripheral 16a - 16f may be a multiple function peripheral, i.e. multiple functions mapping to a single bus connection point serviced by a bus interface, e.g. 22b. Similarly, although not shown, the system unit 12 may support multiple clients.

[0025] Figure 3 illustrates a master/slave model of flow control employed by the present invention for serially interfacing the interconnected peripherals to the system unit and controlling transaction flow. As illustrated, the bus controller 14, the signal bus distributors 18, and the bus interfaces 22 cooperate to implement the master/ slave model of flow control. The bus controller 14 serves as the master, and the signal bus distributors 18 as well as the bus interfaces 22 behave as slave devices to the bus controller 14.

[0026] Under the master/slave model, the bus controller 14 provides flow control for all data communication transactions between the bus agents at their respective operating speeds. The bus interfaces 22 engage in data communication transactions on behalf of the functions of the peripherals 16. However, the bus interfaces 22 accept or transmit data only if they have been authorized or instructed (aka "polled") to do so by the bus controller 14. The bus signal distributors 18 serve strictly as signal distributors. They are merely transparent conduits when data communication transactions are conducted by the bus controller 14 and the bus interfaces 22 on behalf of the bus agents. Thus, the bus signal distributors 18 never actively participate in data communication transactions, accept data or respond with data.

[0027] The bus controller 14 systematically polls the functions of the interconnected peripherals 16 through their bus interfaces 22 for data communication transactions in accordance to a polling schedule which guarantees latencies and bandwidths to the isochronous functions of the interconnected peripherals 16. Polling of the isochronous functions of the interconnected peripherals 16 for data communication transactions are prioritized over for all other polling and as frequent as they are necessary to meet the guaranty. Polling of the asynchronous functions of the interconnected peripherals 16 through their bus interfaces 22 for data communication transactions are scheduled around the polling of the isochronous

functions of the interconnected peripherals **16** for data communication transactions. Preferably, the polling schedule is dynamically adapted to the interconnected peripherals **16** actually present.

[0028] In some embodiments, the bus controller 14, the bus signal distributors 18 and the bus interfaces 22 further engage in connection management transactions employing the same master/slave model for flow control. Similarly, the bus controller 14 provides flow control for conducting the connection management transactions at the serial bus elements' respective operating speeds. The bus signal distributors 18 and the bus interfaces 22 respond to the connection management transactions, replying with control/status information as appropriate. The bus controller 14, during operation, polls the bus signal distributors 18 and the bus interfaces 22 for such transactions. Polling of the bus signal distributors 18 and the bus interfaces 22 for connection management transactions are also scheduled around polling of the isochronous functions of the interconnected peripherals 16 for data communication transactions. Preferably, the expanded polling schedule is also dynamically adapted to the serial bus elements actually present.

[0029] Figure 4 illustrate a frame based polling scheduling of the present invention implemented by some embodiments for conducting the various transactions employing the master/slave model of flow control. As illustrated, the polling schedule 30, also referred to a super frame, comprises of a number of sub-schedules 32, also referred to as soft frames. An isochronous function 34a or 34b of an interconnected peripheral 16 is polled as frequent as it is necessary in one or more soft frames 32 of the super frame 30 to guarantee its latency and bandwidth. However, an asynchronous function 36a or 36b is polled only once in one soft frame 32 of the super frame 30 for data communication transaction. Similarly, an interconnected device 38a or 38b is also polled only once in one soft frame 32 of the super frame 30 for connection management transaction.

[0030] Preferably, all isochronous functions 34a - 34b are polled within a first percentage portion (P1) of a soft frame 32 to ensure the latency and bandwidth guaranties are met. Isochronous functions that cannot be accommodated within P1 are preferably rejected for insufficient capacity. The upper delimiter (M1) of P1 is also referred to as the isochronous watermark. Similarly, all polling are preferably performed within a second percentage portion (P2) of a soft frame 32 to ensure reliability of operation. Multiple soft frames 32 are employed if necessary to accommodate all asynchronous function and serial bus element polling. The upper delimiter (M2) of P2 is also referred to as the frame watermark.

[0031] Various manners in which such a frame based polling schedule may be dynamically generated and updated, are described: in WO/1996/013776, entitled Method And Apparatus For Dynamically Generating And Maintaining Frame Based Polling Schedules That Guarantee Latencies And Bandwidths To Isochronous Func-

tions.

[0032] Figure 5 illustrates geographical and logical addressing of the present invention implemented by some embodiments for addressing the serial bus elements and functions of bus agents. For ease of explanation, the same exemplary serial bus assembly of Figure 2 is used. However, the bus controller 74 is labeled as Host, also referred to as Hub0. The bus signal distributors 18a-18b are labeled as Hub1 and Hub2. The peripherals 16a - 16f including their corresponding bus interfaces 22a - 22f are jointly labeled as Node0 through Node6. The functions of peripherals 16a- 16f are labeled as FN0, FN1, etc.

[0033] As illustrated, the serial bus elements and functions of the bus agents are assigned geographical as well as logical addresses (GEO ADDR & LOG ADDR) of a geographical and a logical address space. More specifically, the Hubs 14, 18a - 18b and the Nodes 22a - 22f are assigned GEO ADDRes, whereas the functions of the Nodes 16a - 16f are assigned LOG ADDRes. Preferably, the Hub identity as well as the upstream port of the Hub may be inferred from the GEO ADDR of a Hub 14, and 18a - 18b, and the connecting Hub as well as the connecting port of the connecting Hub may be inferred from the GEO ADDR of a Node 22a - 22f. In one embodiment, the LOG ADDRes are assigned to the functions of the Nodes 16a - 16f in a chronological manner. [0034] For examples, in the illustrated exemplary application, Hub1 and Hub2 18a and 18b are assigned the GEO ADDRes of "Hub1:Port0" and "Hub2::Port0" respectively, identifying the Hubs 18a and 18b as "Hub1" and "Hub2" respectively, and in each case, the upstream port being "Port0". Node and Node4 22b and 22e are assigned the GEO ADDRes of "Hub1: Port2" and "Hub2: Port3" respectively, identifying the connecting Hubs 18a and 18b as "Hub1" and "Hub2" respectively, and the connecting ports of connecting Hubs 18a and 18b as "Port2" and "Port3" respectively. The functions of Node1 16b are assigned the LOG ADDRes of "LA1", "LA2" and "LA3", whereas the function of Node4 16e is assigned the LOG ADDR of "LA6".

[0035] Preferably, the GEO ADDRes and the LOG ADDRes are dynamically assigned at power on or reset, and updated in response to live detachment of interconnected devices or attachment of additional devices, by the bus controller 14 in cooperation with the bus signal distributors 18 and the bus interfaces 22. A particular implementation of such dynamic connection management is described in more detail below.

[0036] For these embodiments, the GEO ADDRes are used to conduct connection management transactions among the serial bus elements, whereas the LOG ADDRes are used to conduct data communication transactions among the functions of the bus agents The separation of the two types of transactions into the two separate address spaces facilitate dynamic connection management of the serial bus elements, without having to interrupt services to the functions of the bus agents.

[0037] Figure 6 illustrates the essential elements of communication packets of the present invention implemented by some embodiments for conducting the various transactions employing the master/slave model of flow control. For these embodiments, packet identifiers 44 are employed to differentiate control packets from data packets. Control packets are packets employed by the bus controller 14 to authorize or instruct the bus signal distributors 18 and the bus interfaces 22 to engage in transactions. Control packets may also include packets employed by the bus signal distributors 18 and the bus interfaces 22 to acknowledge authorizations or instructions from the bus controller 14. Furthermore, addresses 46 are employed as appropriate to identify the transaction parties. As will be appreciated that under the master/ slave model of flow control, the bus controller 14 as a transaction participant may often be inferred, and therefore its address may be omitted.

[0038] Preferably, transaction flows, such as from bus controller 14 to a function, from a first function to a second function, may be inferred from the packet identifiers 44. Preferably, either geographical or logical addresses 46, i.e. "HubX:PortY" or "LAz", may be specified to accommodate those embodiments that support connection management transactions and implement both types of addresses.

[0039] A particular implementation of employing such communication packets to conduct the various transactions is described in WO/1996/013778, entitled Method And Apparatus For Exchanging Data, Status And Commands Over An Hierarchical Serial Bus Assembly Using Communication Packets.

[0040] Figures 8-9 illustrate one embodiment of the bus controller of the present invention. In this embodiment, the bus controller 14 includes a control state machine and circuitry 52, control/status registers 54, data buffers 56, and bus controller software services 58. The control/status registers 54 are used to store the various control and status data. For examples, the serial bus elements present, their interconnection topology, the functions of the various interconnected peripherals, the geographical addresses assigned to the serial bus elements, the logical addresses assigned to the functions of the interconnected peripherals. The data buffers 56 are used to buffer the data of the data communication transactions between the bus agents. The control state machine and circuitry 52 operates the hardware, controlling data communication transactions and employing the above described master/slave model of flow control, under the programming of the bus controller software services 58. For some embodiments, the control state machine and circuitry 52 further operates the hardware, controlling connection management transactions, implementing the master/slave model of flow control with frame based polling schedule, employing geographical and logical addressing, supporting communication packet based transactions, and/or inference of data and control states from states of the propagation electrical signals. In particular,

the control and state machine circuitry **52** causes the bus controller **14** to cooperate with the bus signal distributors **18** and the bus interfaces 22, and perform the dynamic connection management steps of the present invention, which will be described in more below.

[0041] The bus controller software services 58 program the control state machine and circuitry 52 responsive to the operating system 60 and other software such as device and configuring software 62 and 64 of the system unit 12. In particular, the services include connection management such as detection of serial bus elements present, detection of their interconnection topology, detection of the functions of the interconnected peripherals, and assignment of the geographical and logical addresses. The services further include transaction management such as generation and maintenance of the Polling schedule, polling of the serial bus elements and functions of the bus agents, acknowledgment of certain responses of the serial bus elements and functions of the bus agents, and exchange of data with functions of the bus agents.

[0042] For a more detailed description of the bus controller hardware and the bus controller software services 58, refer to WO/1996/013778, WO/1996/013776 and US 5,742,847. It should be noted that the allocation of functions to the hardware and software services of the bus controller 14 is implementation dependent. The present invention may be practiced with any number of allocations, ranging from minimal hardware usage to minimal employment of software services.

[0043] Figures 10-11 illustrate one embodiment of the bus signal distributor of the present invention. The illustrated embodiment is a 1:7 bus signal distributor 18' having control circuitry 66, control registers 68, and 8 ports 24. Port 0 24 is used to connect the bus signal distributor 18' upstream to the bus controller 14 or another bus signal distributor 18. Ports 1 - 7 are used to connect up to a total of 7 bus signal distributors 18 and/or bus interfaces 22 to itself. The control registers 68 are used to store its own control and status information such as whether a port 24 has a bus interface 22 connected to it or not, and whether the port 24 is turned ON/OFF. The control circuitry 66 operates the bus signal distributor 18' responsive to instructions from the bus controller 14. In particular, the control circuitry 66 causes the bus signal distributor 18 to cooperate with the bus controller 14, and perform the dynamic connection management steps of the present invention, which will be described in more detail below.

[0044] In embodiments where the low cost two signal wire cables 20 are used to interconnect the serial bus elements, and electrical signals are preferably propagated in a differential manner, each port 24 comprises two differential amplifiers 70 and 72 for generating the differential signals. Preferably, each port 24 further having two resistors 74 coupled to ground as shown, pulling the signals on the two wires to ground, thereby allowing the absence or presence of a connected bus interface 22 to

be discernible. The appropriate values of resistors **74** may be determined empirically depending on individual implementations.

[0045] Figures 12-13 illustrate one embodiment of the bus interfaces of the present invention. For this embodiment, the bus interface 22 comprises control circuitry 80, control/status registers 82, a Connector interface 84 and two FIFOs 76 - 78, a Receive FIFO 76 and a Send FIFO 78. Receive and Send FIFOs 76 - 78 are used to stage the receive and send data for data communication transactions. The control/status registers 68 are used to store its own control and status information such as its assigned geographical address, functions of its "host" peripheral, and their assigned logical addresses. The control circuitry 66 operates the bus interface 22 on behalf of the "host" peripheral and the "host" peripheral's functions, responsive to authorizations and instructions from the bus controller 14. In particular, control circuitry 66 causes the bus interface 22 to cooperate with the bus controller 14, and perform the dynamic connection management steps of the present invention, which will be described in more detail below.

[0046] In embodiments where the low cost two signal wire cables 20 are used to interconnect the serial bus elements, and electrical signals are preferably propagated in a differential manner, the Connector interface 84 comprises two differential amplifiers 86 and 88 for generating the differential signals. Preferably, the Connector interface 84 further includes two resistors 90 coupled to Vcc as shown, pulling the signals on the two wires to Vcc complementary to the port circuitry of a connecting bus signal distributor 18. The appropriate values of resistors 90 may also be determined empirically depending on individual implementations.

[0047] For a more detailed description of the bus interface 22, refer to WO/1996/013776, WO/1996/013778 and US 5,742,847.

#### **Dynamic Connection Management**

[0048] Having now described the hierarchical serial bus assembly 26 and the manner its elements cooperate to serially interface the isochronous and asynchronous peripherals 16 to the system unit 12 of the exemplary computer system 10, the dynamic connection determination and management steps of the present invention performed by the serial bus elements of such hierarchical serial bus assembly will now be described in detail.

[0049] Figure 14 illustrates an hierarchical view of the serial bus elements of the present invention employed by the bus controller 14 for determining and managing connection topology. As illustrated, the hierarchy 200 of serial bus elements is logically divided into tiers 202a - 202e. The bus controller 14 and the system unit 12, labeled as Host or Hub0, is considered logically occupying a root tier. The first bus signal distributor 18d connected to the bus controller 14, labeled as Hub1, is considered logically occupying a tier zero. The second bus signal

distributor 18e, the first and second bus interface 22g22h and their "host" peripherals 16g-16h connected to

the first bus signal distributor 18d, labeled as Hub2,

Node0 and Node1 respectively, are considered logically

occupying a tier one. The third and fourth bus signal distributors 18f-18g, the third and fourth bus interface 22i22j and their "host" peripherals 16i-16j connected to the

second bus signal distributor 18e, labeled as Hub3,

Hub4, Node2 and Node3 respectively, are considered

logically occupying a tier two. Lastly, the fifth, sixth and

seventh bus interface 22k-22m and their "host" peripherals 16k-15m connected to the third and fourth bus signal distributors 18f-18g, labeled as Node4, Node5 and

Node6 respectively, are considered logically occupying

a tier three

[0050] While the hierarchical view of serial bus elements is being illustrated with five logical tiers, it will be appreciated that the number of logical tiers is limited only by the physical characteristics of the serial bus elements. In one embodiment, the hierarchical serial bus assembly 16 consists as many as seven logical tiers. It will be appreciated that the present invention may be practiced with less or more logical tiers.

[0051] Figures 15a-15c illustrate the collective method steps of the present invention performed by the serial bus elements for determining and managing connection topology at power on or reset, employing the hierarchical view of the serial bus elements. As illustrated in Figure 15a, at power on or reset, event 204, all bus signal distributors 18 and all bus interfaces 22 initialize themselves with a predetermined default initialization GEO ADDR, e.g. "000:000" for "Hub0" and "Port0", step 206. Furthermore, all bus signal distributors 18 enable their upstream connection port, e.g. port 0, and disable all other ports, step 208. Next, the bus controller 14 in cooperation with the bus signal distributors 18 and the bus interfaces 22 perform geographic initialization of the serial bus assembly 26, step 210.

[0052] Figure 15b illustrates the method steps of the present invention performed by the bus controller 14 for geographically initializing the serial bus assembly 26. Initially, the bus controller 14 selects logical tier zero, step 216. The bus controller 14 then detects if any serial bus element is connected to itself, step 218. If a serial bus element is connected, the bus controller 14 causes the serial bus element to identify itself, i.e. whether it is a bus signal distributor 18 or a bus interface 22, step 218. When instructed to do so, the connected bus signal distributor 18 or bus interface 22 responds accordingly, step 218. The bus controller 14 then assigns a GEO ADDR to the connected serial bus element, step 218.

[0053] In embodiments where the bus controller 14 supports communication packet based transactions, the bus controller 14 sends out a "Presence Query" transaction using the predetermined default initialization GEO ADDR. Recall that all serial bus elements initialize themselves as if they have been assigned the default initialization GEO ADDR, and furthermore all bus signal dis-

tributors 18 enable only their upstream port 24, and disable all other ports, thus only the first serial bus element directly connected to the bus controller 14 will "hear" the "Presence Query" transaction sent out by the bus controller 14. Therefore, only the first serial bus element will respond, allowing the bus controller 14 to discern whether a serial bus element is connected to itself.

[0054] The bus controller 14 in turn sends out an "Identification" transaction still using the predetermined default initialization GEO ADDR, requesting the first serial bus element to identify whether it is a bus signal distributor 18 or a bus interface 22. For the same reason, the first serial bus element will be the only serial bus element detecting that it is the addressee of the "Identify" transaction, and responds with the identification information accordingly. The bus controller 14 then sends out a "GEO ADDR Assignment" transaction still using the predetermined default initialization GEO ADDR, assigning a new GEO ADDR to the first serial bus element, e.g. "001:000" for "Hub1" and "Port0". The first serial bus element, still being the only serial bus element "hearing" the transaction, updates its GEO ADDR accordingly. Preferably, the first serial bus element will acknowledge the address assignment.

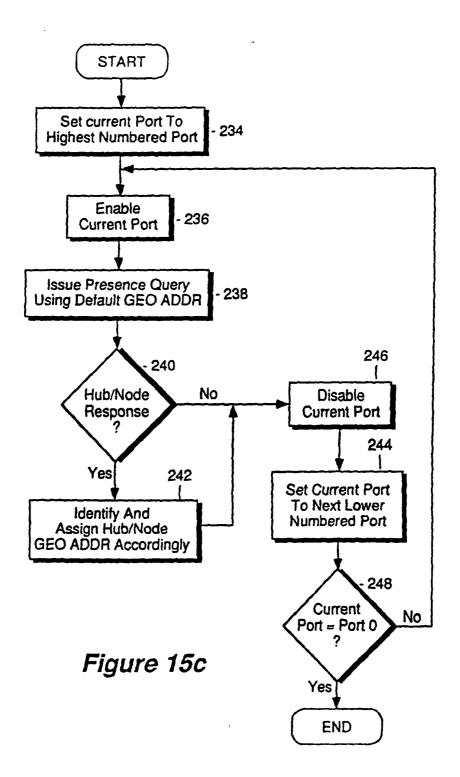

[0055] If the first serial bus element identifies itself as a bus interface 22, step 220, we have the degenerated case of a single connected peripheral. Geographical initialization is completed then. On the other hand, if the first serial bus element identifies itself as a bus signal distributor 18, step 220, the bus controller 14 proceeds to detect whether any serial bus elements are connected to the ports of the first bus signal distributor 18, step 222. [0056] Figure 15c illustrates the method steps of the present invention performed by the bus controller 14 for detecting the presence of connected bus signal distributors 18 and/or bus interfaces 22 at the various ports of a bus signal distributor 18. For ease of explanation, these method steps are illustrated with embodiments where the bus signal distributor ports 24 are "numbered". Furthermore, the upstream port is the lowest numbered port, i.e. port zero, and the highest numbered port is predetermined. However, based on the description to follow, it will be appreciated that the present invention may be practiced with other manner of port identification, as long as the port identification information are provided to the bus controller 14 as part of the earlier described identification process.

[0057] The bus controller 14 sets a current port pointer to the highest numbered port of the bus signal distributor of interest, step 234. The bus controller 14 then instructs the bus signal distributor of interest to enable the current port, i.e. the highest numbered port at this time, step 236. The bus controller 14 then detects if any serial bus element is connected to the particular port of the bus signal distributor of interest, step 238. If a serial bus element is not connected, the bus controller 14 disables the particular port of the bus signal distributor of interest, step 244. If a serial bus element is connected, the bus controller

14 causes the connected serial bus element to identify itself, and assigns a GEO ADDR to the connected serial bus element accordingly, step 242, before disabling the particular port of the bus signal distributor of interest, step 244.

[0058] Again, in embodiments where the bus controller 14 supports communication packet based transactions, at step 238, the bus controller 14 sends out a "Presence Quern" transaction using the predetermined default initialization GEO ADDR. For the same reason discussed earlier, only the serial bus element connected to the particular port of the bus signal distributor of interest will "hear" the "Presence Query" transaction sent out by the bus controller 14. Therefore, only this serial bus element will respond, allowing the bus controller 14 to discern whether a serial bus element is connected to the particular port of the bus signal distributor of interest.

[0059] The bus controller 14 then follows with an "Identification" transaction, and a "GEO ADDR Assignment" transaction, using the predetermined default initialization GEO ADDR, as described earlier, thereby causing the newly detected serial bus element to be identified and assigned with a new GEO ADDR. Preferably, a bus interface 22 will also respond with the functions of its "host" peripheral as an integral part of its reply to the "Identify" transaction. Alternatively, a separate function identification transaction may be performed.

[0060] Continuing now with Figure 15c, upon disabling the particular port of the bus signal distributor of interest, the bus controller 14 sets the current port pointer to the next lower numbered port, step 246. If the updated current port pointer is not pointing to the upstream port, step 248, the bus controller 14 enables the particular port of the bus signal distributor of interest, and performs the detection, identification, and GEO ADDR assignment as described earlier. If the updated current port pointer is pointing to the upstream port, step 248, geographical initialization is completed.

[0061] Returning back to Figure 15a, upon completing geographic initialization, step 210, the bus controller 14 in cooperation with the bus interfaces 22 performs logical initialization, step 212. More specifically, if "host" peripheral function identification has not been performed as an integral part of the geographical initialization process, the bus controller 14 systematically polls the bus interfaces 22 for the information. Upon learning all the functions of the "host" peripherals, the bus controller 14 assigns LOG ADDRes to the identified functions, step 212. In some embodiments, the logical addresses are assigned chronologically, e.g. LA0 for FN0, LA1 for FN1, etc. etc.

[0062] Lastly, for embodiments where the bus controller 14 dynamically generates and updates its polling schedule, the bus controller 14 generates its polling schedule of the serial bus elements including systematic polling to detect attachment or detachment of serial bus elements, step 214. The detection of attachment or detachment of serial bus elements is performed with connection management transactions in like manner as de-

tection for presence of connected serial bus elements at the various ports **24** of a bus signal distributor **18** performed during geographical initialization. As described earlier, polling of serial bus elements for connection management transactions are scheduled around the polling of isochronous functions for data communication transactions. Preferably, the information necessary to generate and maintain the polling schedule dynamically is collected as part of the identification process, post geographical initialization, or also an integral part of geographical initialization.

[0063] Figure 16 illustrates the collective method steps of the present invention performed by the serial bus elements for managing connection topology during operation. As illustrated, upon successful completion of connection topology determination and management activities at power on or set, the bus controller 14 proceeds to poll the serial bus elements and bus agent functions in accordance to the polling schedule, step 216. As described earlier, the polling schedule includes polling for connection management transactions that facilitate the detection of detachment of connected serial bus elements, or attachment of additional serial bus elements. If attachment or detachment of serial bus elements is detected, step 218, the bus controller 14 performs complete/partial geographical and logical reinitializations in like manner as geographical and logical initialization is performed during power on or reset. Preferably partial reinitializations are always performed as long as a function of an interconnected peripheral 16 still requires interaction with the system unit 12. Recall that polling for connection transaction management is scheduled around polling of the isochronous as well as asynchronous functions of the interconnect peripherals 16 for data communication transactions, thus partial reinitialization may be performed without having to interrupt servicing of the isochronous and asynchronous functions of the interconnected peripherals 16.

**[0064]** Thus, a method and apparatus for dynamically managing connection topology of an hierarchical serial bus assembly has been described.

[0065] While the present invention has been described in terms of the above embodiments, those skilled in the art will recognize that the invention is not limited to the embodiments described. The method and apparatus of the present invention can be practiced with modification and alteration within the scope of the appended claims. The description is thus to be regarded as illustrative instead of limiting on the present invention.

#### Claims

An apparatus for dynamically determining and managing connection topology of a serial bus assembly (26) including a bus controller (14), zero or more bus signal distributors (18, 18a-18b), and one or more bus interfaces (22, 22a-f) for hierarchically intercon-

necting one or more peripherals (16, 16a-f) to a system unit of a computer system, **characterized by** the apparatus comprising:

a first means for initializing (206) each bus signal distributor (18, 18a-18b), of the zero or more bus signal distributors (18, 18a-18b) and each of the one or more bus interfaces (22, 22a-f) with a predetermined default common geographical address at power on/reset (204);

a second means having the bus controller (14) for enabling (208) an upstream port (24) and for disabling (208) all other ports (24) of each of the zero of more bus signal distributors (18, 18a-18b) at power on/reset; and

a third means (66), coupled to the first and second means, for facilitating the bus controller (14), coupled with the bus signal distributors (18, 18a-18b),

employ a logical hierarchical view (200) of the serial bus assembly (26);

electively instruct to enable, one port at a time, based on the logical hierarchical view, all the disabled other ports (24) of the zero or more bus signal distributors (18, 18a-18b) at power on/reset,

incrementally detect each of the zero or more bus signal distributors (18, 18a-18b) and the one or more bus interfaces (22, 22a-f), and

replace (210), in response to the detecting, the predetermined default common geographical address with a unique geographical address to each of the detected zero or more bus signal distributors (18, 18a-18b) and the one or more bus interfaces (22, 22a-f) at power on/reset and periodically during operation.

- 2. The apparatus of claim 1, wherein the bus controller (14) is operable to instruct the zero or more bus signal distributors (18, 18a-18b) to replace the predetermined default common geographical address with a unique geographical address for conducting confection management transactions among the one or more peripherals (16, 16a-16f).

- 3. The apparatus of claim 1, wherein the bus controller (14) is operable to instruct the bus interface (22) to replace the predetermined default common geographical address with a unique geographical address for conducting connection management transactions among the one or more peripherals (16, 16a-16f).

- **4.** The apparatus of claim 1, wherein the bus controller (14) determines a count of functions supported by the one or more peripherals (16, 16a-16f).

- 5. The apparatus of claim 4, wherein the bus controller

40

45

50

(14) assigns a unique logical address to each function counted.

- **6.** The apparatus of claim 1, wherein the bus controller (14) is operable to instruct the zero or more bus signal distributors (18, 18a-18b) to selectively enable the disabled ports (24).

- 7. The apparatus of claim 6, wherein the zero or more bus signal distributors (18, 18a-18b) communicate with the bus controller (14) via the upstream port (24).

- 8. The apparatus of claim 1, wherein the zero or more bus signal distributors (18, 18a-18b) are coupled with the one or more bus signal distributors (18, 18a-18b) that communicate with the bus signal distributor via the one or more upstream ports (24) of the zero or more bus signal distributors.

- 9. The apparatus of claim 1, wherein the one or more bus signal distributors (18, 18a-18b) are coupled with the one or more peripherals (16, 16a-16f) via the one or more bus interfaces (22, 22a-22f).

- **10.** The apparatus of claim 1, wherein the one or more peripherals (16, 16a-16f) are hot swappable.

- 11. The apparatus of claim 1, wherein the one of more peripherals (16, 16a-16f) are isochronous and asynchronous peripherals, and wherein the bus controller (14) determines latencies and bandwidths for the isochronous peripherals.

- 12. A method for dynamically determining and managing connection topology of a serial bus assembly (26) including a bus controller (14), zero or more bus signal distributors (18, 18a-18b), and one or more bus interfaces (22, 22a-f) for hierarchically interconnecting one or more peripherals to a system unit of a computer system characterized by the method comprising:

initializing (206), by first means, each bus signal distributor (18, 18a-18b) of the zero or more bus signal distributors (18, 18a-18b) and each of the one or more bus interfaces (22, 22a-22f) with a predetermined default common geographical address at power on/reset (204);

enabling (208), by second means having the bus controller (14), an upstream port (24) and disabling (208) all other ports (24) of each of the zero or more bus signal distributors (18, 18a-18b) at power on/reset;

employing a logical hierarchical view (200) of the serial bus assembly (26);

selectively enabling the disabled ports (24), one port at a time, based on the logical hierarchical view of the serial bus assembly, at power on/

reset:

incrementally detecting each of the zero or more bus signal distributors (18, 18a-18b) and the one or more bus interfaces (22, 22a-22f); and replacing (210), in response to the detecting, the predetermined default common geographical address with a unique geographical address to each of the detected zero or more bus signal distributors (18, 18a-18b) and the one or more bus interfaces at power on/reset and periodically during operation.

- 13. The method in claim 12, wherein initializing (206) the zero or more bus signal distributors (18, 18a-18b) and the one or more bus interfaces (22, 22a-22f) at power on/reset includes self-initializing the zero or more bus signal distributors (18, 18a-18b) and the one or more bus interfaces (22, 22a-22f) with the predetermined default common geographical addresses.

- **14.** The method in claim 12, further comprising determining, by the bus controller (14), a count of functions (34a-34b) associated with the one or more peripherals (16, 16a-16f).

- The method in claim 13, further comprising assigning logical addresses based on the determined count of functions (34a-34b).

#### Patentansprüche

35

40

Vorrichtung zur dynamischen Bestimmung und Verwaltung einer Verbindungstopologie einer seriellen Busvorrichtung (26) einschließlich einer Bussteuerung (14), null oder mehreren Bussignalverteilern (18, 18a-18b) und einer oder mehrerer Busschnittstellen (22, 22a-f) zum hierarchischen Zusammenschalten von einem oder mehreren Peripheriegeräten (16,16a-f) mit einer Systemeinheit eines Computersystems, dadurch gekennzeichnet, dass die Vorrichtung Folgendes umfasst:

ein erstes Mittel zum Initialisieren (206) jedes Bussignalverteilers (18, 18a-18b) der null oder mehreren Bussignalverteiler (18, 18a-18b) und jeder der einen oder mehreren Busschnittstellen (22, 22a-f) mit einer vorgegebenen allgemeinen geografischen Standardadresse bei Leistung ein/Rückstellung (204);

ein zweites Mittel, das die Bussteuerung (14) aufweist, um einen stromaufwärtigen Port (24) zu aktivieren (208) und alle anderen Ports (24) von jedem der null oder mehreren Bussignalverteiler (18, 18a-18b) bei Leistung ein/Rückstellung zu deaktivieren (208); und

ein drittes Mittel (66), das mit dem ersten und

zweiten Mittel zur Unterstützung der Bussteuerung (14) gekoppelt ist, die mit den Bussignalverteilern (18, 18a-18b) gekoppelt ist, damit sie:

eine logische hierarchische Ansicht (200) der seriellen Busvorrichtung (26) verwendet; selektiv anweist, auf der Grundlage der logischen hierarchischen Ansicht alle deaktivierten anderen Ports (24) der null oder mehreren Bussignalverteiler (18, 18a-18b) bei Leistung ein/Rückstellung zu aktivieren, und zwar einen Port auf einmal;

jeden der null oder mehreren Bussignalverteiler (18,18a-18b) und jede der einen oder mehreren Busschnittstellen (22, 22a-f) inkrementell erfasst, und

die vorgegebene allgemeine geografische Standardadresse in Ansprechung auf die Erfassung bei jedem der erfassten null oder mehreren Bussignalverteiler (18, 18a-18b) und der einen oder mehreren Busschnittstellen (22, 22a-f) bei Leistung ein/Rückstellung und regelmäßig während des Betriebs durch eine eindeutige geografische Adresse ersetzt (210).

- 2. Vorrichtung nach Anspruch 1, wobei die Bussteuerung (14) dazu betriebsfähig ist, die null oder mehreren Bussignalverteiler (18, 18a-18b) anzuweisen, die vorgegebene allgemeine geografische Standardadresse durch eine eindeutige geografische Adresse zum Ausführen von Verbindungsverwaltungstransaktionen zwischen dem einen oder den mehreren Peripheriegeräten (18, 16a-16f) zu ersetzen.

- 3. Vorrichtung nach Anspruch 1, wobei die Bussteuerung (14) dazu betriebsfähig ist, die Busschnittstelle (22) anzuweisen, die vorgegebene allgemeine geografische Standardadresse durch eine eindeutige geografische Adresse zum Ausführen von Verbindungsverwaltungstransaktionen zwischen dem einen oder den mehreren Peripheriegeräten (16, 18a-16f) zu ersetzen.

- 4. Vorrichtung nach Anspruch 1, wobei die Bussteuerung (14) eine Zählung der Funktionen bestimmt, die von dem einen oder den mehreren Peripheriegeräten (16, 16a-16f) unterstützt wird.

- Vorrichtung nach Anspruch 4, wobei die Bussteuerung (14) jeder gezählten Funktion eine eindeutige logische Adresse zuweist.

- 6. Vorrichtung nach Anspruch 1, wobei die Bussteuerung (14) dazu funktionsfähig ist, die null oder mehreren Bussignalverteiler (18, 18a-18b) anzuweisen, die deaktivierten Ports (24) selektiv zu aktivieren.

- 7. Vorrichtung nach Anspruch 6, wobei die null oder mehreren Bussignalverteiler (18, 18a-18b) mit der Bussteuerung (14) über den stromaufwärtigen Port (24) kommunizieren.

- 8. Vorrichtung nach Anspruch 1, wobei die null oder mehreren Bussignalverteiler (18, 18a-18b) mit dem einen oder den mehreren Bussignalverteilern (18, 18a-18b) gekoppelt sind, die mit dem Bussignalverteiler über den einen oder die mehreren stromaufwärtigen Ports (24) der null oder mehreren Bussignalverteiler kommunizieren.

- Vorrichtung nach Anspruch 1, wobei der eine oder die mehreren Bussignalverteiler (18, 18a-18b) mit dem einen oder den mehreren Peripheriegeräten (16, 16a-16f) über die eine oder die mehreren Busschnittstellen (22, 22a-22f) gekoppelt sind.

- 20 10. Vorrichtung nach Anspruch 1, wobei das eine oder die mehreren Peripheriegeräte (18, 16a-16f) im laufenden Betrieb auswechselbar sind.

- 11. Vorrichtung nach Anspruch 1, wobei das eine oder die mehreren Peripheriegeräte (16, 16a-16f) isochrone und asynchrone Peripheriegeräte sind und wobei die Bussteuerung (14) Latenzen und Bandbreiten für die isochronen Peripheriegeräte bestimmt.

- 12. Verfahren zur dynamischen Bestimmung und Verwaltung einer Verbindungstopologie einer seriellen Busvorrichtung (26) einschließlich einer Bussteuerung (14), null oder mehreren Bussignalverteilern (18, 18a-18b) und einer oder mehrerer Busschnittstellen (22, 22a-f) zum hierarchischen Zusammenschalten von einem oder mehreren Peripheriegeräten mit einer Systemeinheit eines Computersystems, dadurch gekennzeichnet, dass das Verfahren Folgendes umfasst:

Initialisieren (206) jedes Bussignalverteilers (18, 18a-18b) der null oder mehreren Bussignalverteiler (18, 18a-18b) und jeder der einen oder mehreren Busschnittstellen (22, 22a-f) durch ein erstes Mittel mit einer vorgegebenen allgemeinen geografischen Standardadresse bei Leistung ein/Rückstellung (204);

Aktivieren (208) eines stromaufwärtigen Ports (24) und Deaktivieren (208) aller anderen Ports (24) von jedem der null oder mehreren Bussignalverteiler (18, 18a-18b) durch ein zweites Mittel, das die Bussteuerung (14) aufweist, bei Leistung ein/Rückstellung;

Verwenden einer logischen hierarchischen Ansicht (200) der seriellen Busvorrichtung (26); selektives Aktivieren der deaktivierten Ports (24), und zwar eines Ports auf einmal, auf der

12

45

Grundlage der logischen hierarchischen Ansicht der seriellen Busvorrichtung bei Leistung ein/Rückstellung;

inkrementelles Erfassen von jedem der null oder mehreren Bussignalverteiler (18, 18a-18b) und der einen oder mehreren Busschnittstellen (22, 22a-f); und

in Ansprechung auf die Erfassung, Ersetzen (210) der vorgegebenen allgemeinen geografischen Standardadresse bei jedem der erfassten null oder mehreren Bussignalverteiler (18, 18a-18b) und der einen oder mehreren Busschnittstellen (22, 22a-f) bei Leistung ein/Rückstellung und regelmäßig während des Betriebs durch eine eindeutige geografische Adresse.

- 13. Verfahren nach Anspruch 12, wobei das Initialisieren (206) der null oder mehreren Bussignalverteiler (18, 18a-18b) und der einen oder mehreren Busschnittstellen (22, 22a-22f) bei Leistung ein/Rückstellung die Selbstinitialisierung der null oder mehreren Bussignalverteiler (18, 18a-18b) und der einen oder mehreren Busschnittstellen (22, 22a-22f) mit den vorgegebenen allgemeinen geografischen Standardadressen beinhaltet.

- 14. Verfahren nach Anspruch 12, weiterhin umfassend das Bestimmen einer Zählung von Funktionen (34a-34b), die dem einen oder den mehreren Peripheriegeräten (16, 16a-16f) zugeordnet sind, durch die Bussteuerung (14).

- **15.** Verfahren nach Anspruch 13, weiterhin umfassend das Zuweisen logischer Adressen auf der Grundlage der bestimmten Zählung von Funktionen (34a-34b).

#### Revendications

1. Un appareil permettant de déterminer et de gérer dynamiquement la topologie de connexion d'un ensemble de bus série (26) y compris un contrôler de bus (14), zéro ou plusieurs distributeurs de signaux de bus (18g, 18a-18b) et une ou plusieurs interfaces de bus (22g, 22a-f) pour l'interconnexion hiérarchique d'un ou plusieurs périphériques (16g, 16a-f) à une unité d'un système informatique se caractérisant par le fait que l'appareil comprend ce qui suit :

un premier moyen pour initialiser (206) chaque distributeur de signaux de bus (18, 18a-18b) des zéro ou plusieurs distributeurs de signaux de bus (18, 18a-18b) et chacune de la ou des interfaces de bus (22, 22a-f) avec une adresse géographique commune par défaut prédéterminée à la mise en marche/réinitialisation (204); un deuxième moyen utilisant le contrôleur de bus (14) pour activer (208) un port en amont (24)

et pour désactiver (208) tous les autres ports (24) de chacun des zéro ou plusieurs distributeurs de signaux de bus (18, 18a-18b) à la mise en marche/réinitialisation ; et

un troisième moyen (66), raccordé aux premier et deuxième moyens, pour faciliter le contrôleur de bus (14), raccordé aux distributeurs de signaux de bus (18, 18a-18b) pour:

employer une vue hiérarchique logique (200) de l'ensemble de bus série (26) ; demander sélectivement l'activation, un port à la fois, selon la vue hiérarchique logique, de tous les autres ports désactivés (24) des zéro ou plusieurs distributeurs de signaux de bus (18, 18a-18b) à la mise en marche/réinitialisation; détecter de manière incrémentielle chacun des zéro ou plusieurs distributeurs de signaux de bus (18, 18a-18b) et de la ou des interfaces de bus (22-22a-f); et remplacer (210), en réponse à la détection, l'adresse géographique commune par défaut prédéterminée par une adresse géographique unique, à chacun des zéro ou plusieurs distributeurs de signaux de bus détectés (18, 18a-8b) et de la ou des interfaces de bus (22, 22a-f) à la mise en marche/réinitialisation et périodiquement en

2. L'appareil de la revendication 1, dans lequel le contrôleur de bus (14) peut demander aux zéro ou plusieurs distributeurs de signaux de bus (18, 18a) de remplacer l'adresse géographique commune par défaut prédéterminée par une adresse géographique unique pour la réalisation des transactions de gestion de connexion sur le ou les périphériques (16, 16a-16f).

cours de fonctionnement.

- 3. L'appareil de la revendication 1, dans lequel le contrôleur de bus (14) peut demander à l'interface de bus (22) de remplacer l'adresse géographique commune par défaut prédéterminée par une adresse géographique unique pour la réalisation des transactions de gestion de connexion sur le ou les périphériques (16, 16a-16f).

- L'appareil de la revendication 1, dans lequel le contrôleur de bus (14) détermine un nombre de fonctions prises en charge par le ou les périphériques (16, 16a-16f).

- 5. L'appareil de la revendication 4, dans lequel le contrôleur de bus (14) attribue une adresse logique unique à chaque fonction dénombrés.

- 6. L'appareil de la revendication 1, dans lequel le con-

50

35

trôleur de bus (14) peut demander aux zéro ou plusieurs distributeurs de signaux de bus (18, 18a-18b) d'activer de manière sélective les ports désactivés (24).

- 7. L'appareil de la revendication 6, dans lequel les zéro ou plusieurs distributeurs de signaux de bus (18, 18a-18b) communiquent avec le contrôleur de bus (14) via le port en amont (24).

- 8. L'appareil de la revendication 1, dans lequel les zéro ou plusieurs distributeurs de signaux de bus (18, 18a-18b) sont raccordés au ou aux distributeurs de signaux de bus (18, 18a-18b) qui communiquent avec le distributeur de signaux de bus via le ou les ports en amont (24) des zéro ou plusieurs distributeurs de signaux de bus.

- L'appareil de la revendication 1, dans lequel les zéro ou plusieurs distributeurs de signaux de bus (18, 18a-18b) sont raccordés au ou aux périphériques (16, 16a-16f) via la ou les interfaces de bus (22, 22a-22f).

- **10.** L'appareil de la revendication 1, dans lequel le ou les périphériques (16, 16a-16f) sont remplaçables à chaud.

- 11. L'appareil de la revendication 1, dans lequel le ou les périphériques (16, 16a-16f) sont des périphériques isochrones et asynchrones et dans lequel le contrôleur de bus (14) détermine les temps d'attente et les largeurs de bande des périphériques isochrones.

- 12. Un procédé permettant de déterminer et de gérer de manière dynamique la topologie de connexion d'un ensemble de bus série (26) comprenant un contrôleur de bus (14), zéro ou plusieurs distributeurs de signaux de bus (18, 18a-18b) et une ou plusieurs interfaces de bus (22, 22a-f) pour l'interconnexion hiérarchique d'un ou plusieurs périphériques à une unité d'un système informatique, se caractérisant le fait que le procédé suppose les opérations suivantes :

initialiser (206), par un premier moyen, chaque distributeur de signaux de bus (18, 18a-18b) des zéro ou plusieurs distributeurs de signaux de bus (18, 18a-18b) et chacune de la ou des interfaces de bus (22, 22a-22f) avec une adresse géographique commune par défaut prédéterminée à la mise en marche/réinitialisation (204); activer (208), par un deuxième moyen utilisant le contrôleur de bus (14) un port en amont (24) et désactiver (208) tous les autres ports (24) de chacun des zéro ou plusieurs distributeurs de signaux de bus (18, 18a-18b) à la mise en

marche/réinitialisation;

employer une vue hiérarchique logique (200) de l'ensemble de bus série (26);

activer de manière sélective les ports désactivés (24), un port à la fois, selon la vue hiérarchique logique de l'ensemble de bus série à la mise en marche/réinitialisation;

détecter de manière incrémentielle chacun des zéro ou plusieurs distributeurs de signaux de bus (18, 18a-18b) et de la ou des interfaces de bus (22, 22a-22f); et

remplacer (210), en réponse à la détection, l'adresse géographique commune par défaut prédéterminée par une adresse géographique unique à chacun des zéro ou plusieurs distributeurs de signaux de bus (18, 18a-18b) et interfaces de bus détectés à la mise en marche/réinitialisation et périodiquement en cours de fonctionnement.

- 13. Le procédé de la revendication 12, dans lequel l'initialisation (206) des zéro ou plusieurs distributeurs de signaux de bus (18, 18a-18b) et de la ou des interfaces de bus (22, 22a-22f) à la mise en marche/réinitialisation suppose l'auto-initialisation des zéro ou plusieurs distributeurs de signaux de bus (18, 18a-18b) et de la ou des interfaces de bus (22, 22a-22f) avec les adresses géographiques communes par défaut prédéterminées.

- 14. Le procédé de la revendication 12 supposant également la détermination par le contrôleur de bus (14) du nombre de fonctions (34a-34b) associées au ou aux périphériques (16, 16a-16f).

- **15.** Le procédé de la revendication 13 supposant également d'affecter des adresses logiques selon le nombre de fonctions déterminées (34a-34b).

Figure 3

Figure 8

Figure 9

Figure 14

Figure 15a

Figure 16

#### EP 0 789 867 B1

#### REFERENCES CITED IN THE DESCRIPTION

This list of references cited by the applicant is for the reader's convenience only. It does not form part of the European patent document. Even though great care has been taken in compiling the references, errors or omissions cannot be excluded and the EPO disclaims all liability in this regard.

#### Patent documents cited in the description

- US 5394556 A, Oprescu [0008]

- WO 9415303 A [0009]

- US 5742847 A [0020] [0042] [0047]

- WO 1996013776 A [0031] [0042] [0047]

- WO 1996013778 A [0039] [0042] [0047]